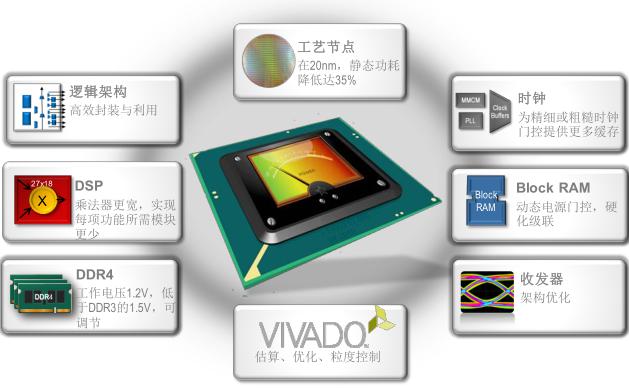

Xilinx UltraScale Architecture: The industry's first ASIC-level programmable architecture that scales from 20nm planar transistor planar processing to 16nm or even FinFET transistor technology, from monolithic to 3D IC expansion. It not only solves the problem of the overall system throughput expansion limit and delay, but also directly addresses the biggest bottleneck in the performance of advanced node chips - interconnection.

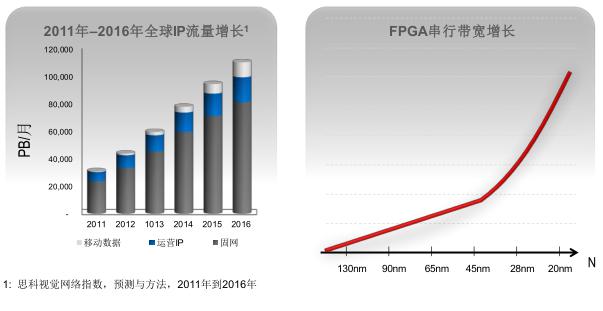

According to the statistics and forecast analysis of the Cisco Vision Network Index, global IP traffic grew rapidly from 2011 to 2016, reaching nearly 60,000 PB/month in 2013, and is expected to approach 120,000 PB per month in 2016. The rapid growth of IP traffic drives the bandwidth and data flow requirements of FPGA devices. The growth of FPGA serial bandwidth is also closely related to process technology, so the demand for process technology is increasing.

ASIC-level programmable architecture solves interconnection problems in four major ways

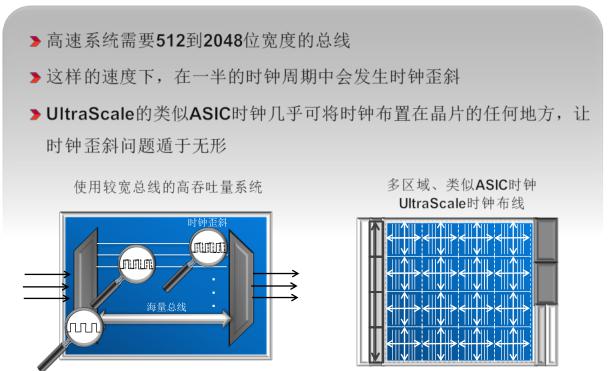

In fact, the UltraScale architecture solves the biggest bottleneck affecting the performance of advanced node chips—wiring—from wiring, clocks, critical paths, and power supplies.

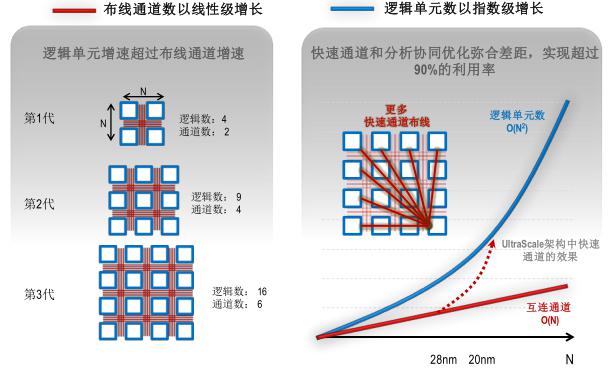

We can use the traffic congestion problem to describe the role of the UltraScale architecture. To put it bluntly, before the UltraScale architecture is used, the limited roads will cause the main line to be blocked. With the UltraScale architecture, as shown in the figure on the right, the new method of realizing the "intelligent traffic flow" is fundamentally Solved the problem of "traffic congestion", that is, interconnection problems.

(1) Adding real and effective routing channels to help cope with increasing complexity

(2) Similar ASIC clock maximizes performance margin for maximum throughput

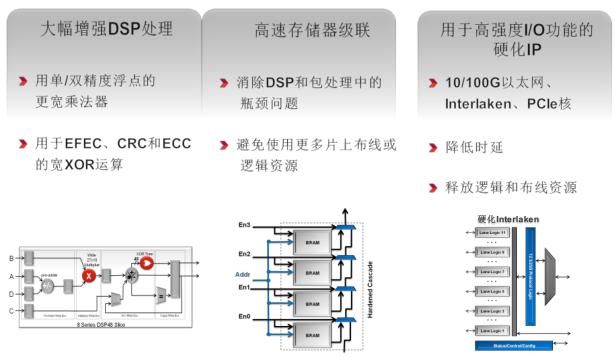

(3) Highly optimized critical path to eliminate bottlenecks in DSP and packet processing

(4) A new generation of power management functions to achieve a leap in performance

Gear Sensor has been widely used in the automotive and industrial field, which is important to the measurement of velocity, angel, angular velocity, direction of rotation.

Gear Sensor,Custom Gear Sensor,Gear Sensor 3 Pins,Good Gear Sensor

Yuheng Optics Co., Ltd.(Changchun) , https://www.yhencoder.com