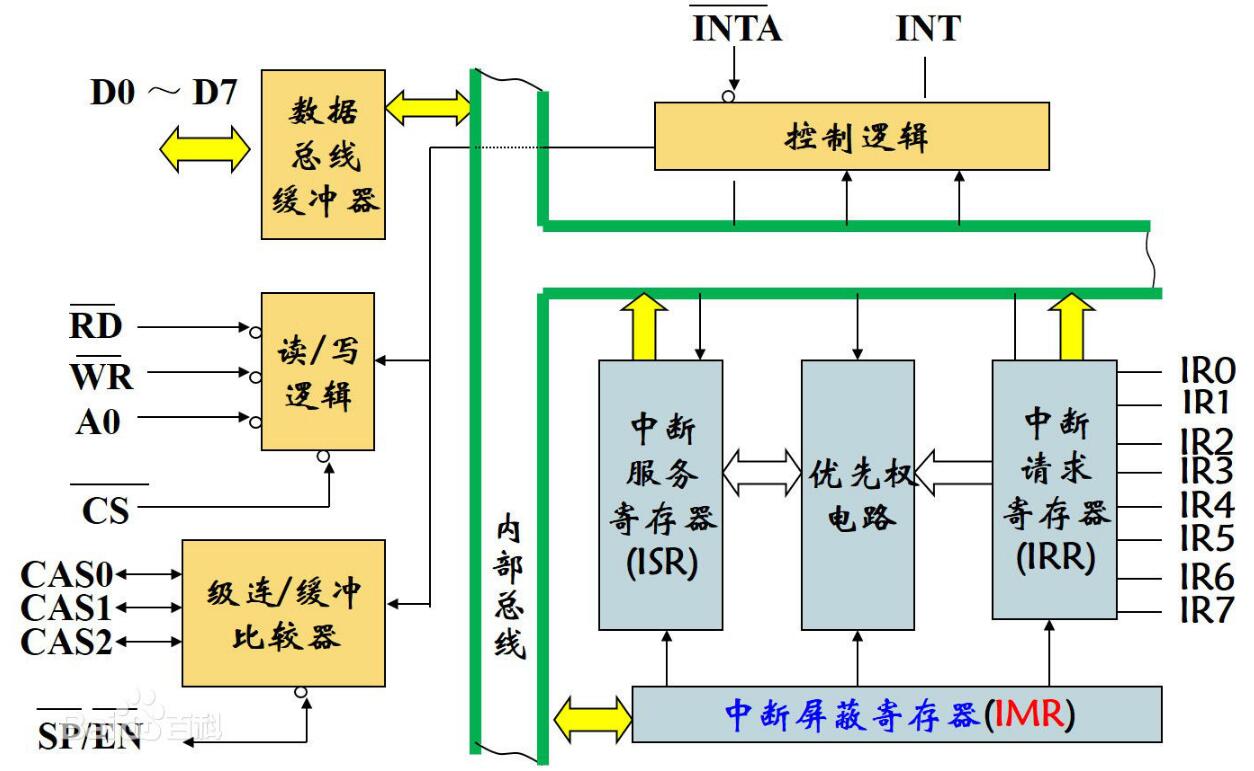

The 8259A is a chip designed specifically for interrupt control of the 8085A and 8086/8088. It is an interrupt controller that can be controlled by a program. A single 8259A can manage 8-level vector priority interrupts. Without adding other circuits, it is possible to cascade up to 64 levels of vector priority interrupt systems. The 8259A has a variety of operating modes that can be used in various systems. Various operating modes are set by software during initialization. Under the control of the bus controller, the 8259A chip can be in a programmed state and an operating state. The programming state is a state in which the CPU initializes the 8259A chip using IN or OUT instructions.

8259A main functionFunction: In a system with multiple interrupt sources, accept external interrupt requests, and judge, select the current highest priority interrupt request, and then send this request to the INTR end of the cpu; when the cpu responds to the interrupt and enters the interrupt After the processing of the subroutine, the interrupt controller is still responsible for managing the external interrupt request.

The main features of the 8259A are as follows:

One 8259A can accept and manage eight levels of maskable interrupt requests, and can be expanded to 63 levels of maskable interrupt priority through eight 8259A cascades.

2 For each level of interrupt can be shielded or allowed by the program.

3 In the interrupt response cycle, the 8259A can provide the CPU with the corresponding interrupt type code.

4 has a variety of working methods, and can be selected by programming.

The 8259A interrupt priority management has two methods: fixed priority and automatic cycle priority.

1) Fixed priority method

In the fixed priority mode, the interrupt priority level of IR7~IR0 is determined by the system.

Their priority order from high to low is: IR0, IR1, IR2, ..., IR7, where IR0 has the highest priority and IR7 has the lowest priority. When there are multiple IRi requests, the priority determiner (PR) compares them with the priority of the interrupt source currently being processed, selects the IRi with the highest priority, and sends an interrupt request INT to the CPU. .

(2) Automatic cycle priority mode

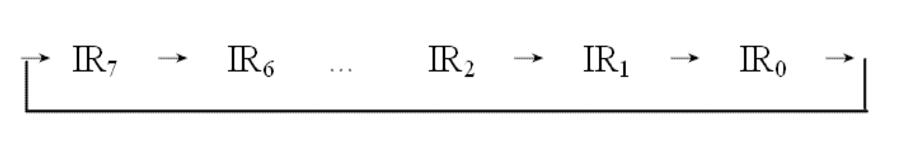

In the automatic cycle priority mode, the IR7~IR0 priority levels can be changed.

The law of change is that when an interrupt request IRi service is completed, the priority of the interrupt is automatically reduced to the lowest priority, and the priority of the immediately following interrupt request IR(i+1) is automatically raised to the highest, IR7 to IR0 priority. The level is changed in a right-circular manner as shown below.

Assuming that there is a request in the initial state IR0, the CPU is serviced, the IR0 priority is automatically reduced to the lowest, after IR7, and the priority of IR1 thereafter is the highest, and the rest is analogized. This kind of priority management method can make all eight interrupt requests have the right to enjoy the same priority service.

In the automatic cycle priority mode, the method of determining the lowest priority in the cycle is different, and it is divided into two types: an ordinary automatic cycle mode and a special automatic cycle mode.

The characteristic of the ordinary automatic circulation mode is that the initial highest priority in IR7~IR0 is specified by the system, that is, the priority of IR0 is designated as the highest, and then the circulation is queued according to the right circulation rule.

The characteristic of the special automatic cycle mode is that the initial lowest priority in IR7~IR0 is specified by the user by setting the priority command.

2. Interrupt nesting8259A interrupt nesting is divided into completely nested and special completely nested two.

(1) Completely nested

Complete nesting is a basic priority management method that the 8259A automatically enters during initialization.

Its characteristics are: interrupt priority management is a fixed mode, ie, IR0 has the highest priority and IR7 has the lowest priority. During CPU interrupt service (ie, during execution of an interrupt service routine), only new interrupt requests are allowed to occur. An interrupt request with the priority "high" of the interrupt request of the current service enters, and the response to the "peer" or "low" interrupt request is prohibited.

(2) special full nesting

The special full nesting method is a basic priority management method used by the 8259A in a multi-slice cascade.

Its characteristics are: interrupt priority management is fixed, IR7 ~ IR0 priority and full nesting rules the same; and completely different from the nested mode is in the CPU interrupt service, in addition to allowing advanced interrupt request, but also allow The same-level interrupt request enters, thus achieving a special nesting of the same-level interrupt request.

In the cascade mode, the main slice is usually set to a special full nesting mode, and the slice is set to be completely nested. When the master piece serves a certain slave interrupt request, the IR7~IR0 requests in the slave chip are all introduced through a certain IRi request in the master piece. Therefore, from the IR7 to IR0 of the slice, they belong to the same level for the main slice IRi. Only when the main slice works in a special complete nesting mode, complete nesting can be achieved from the slice.

3. Interrupt masking methodThe interrupt masking method is an interrupt management method for the external interrupt source IR7~IR0 of the 8259A. There are two types of interrupt protection methods: ordinary shielding and special shielding.

(1) Ordinary shielding

The general shielding method is to shield the interrupt request IRi through the 8259A interrupt mask register (IMR). By programming the write operation command word OCW1, the Di in the IMR is set to 1 to mask the IRi (i=0 to 7) interrupt request.

(2) special shielding

The special masking mode allows low-priority interrupt requests to interrupt high-priority interrupts that are being serviced. This masking method is usually used for the master chip in the cascade mode. For a case where multiple interrupt sources are connected to the same request IRi, it can be set or canceled by programming the operation command word OCW3.

In the special masking mode, you can use the interrupt masking command in the interrupt service subroutine to mask the current interrupt being processed, and at the same time, clear the corresponding bit in the ISR corresponding to the current interrupt, which not only shields the current processing. Interruptions, but also really open lower level interrupt requests.

In this case, although the CPU still continues to execute higher-level interrupt service routines, the corresponding bit in the ISR corresponding to the current interrupt has been cleared as if it did not respond to the interrupt. Therefore, for lower level interrupt requests, the 8259A can still generate INT interrupt requests and the CPU will respond to lower level interrupt requests.

4. Interrupt end methodThe end of interrupt mode means that the CPU should clear the interrupt service flag in time after the service is completed for an interrupt request. Otherwise, it means that the interrupt service is still continuing, so that the interrupt request whose priority is lower than the interrupt request cannot be responded to. The interrupt service flag is stored in the interrupt service register (ISR). When an interrupt source IRi is responded, the Di bit in the ISR is set to 1 and the service is cleared in time.

The 8259A provides the following three interrupt termination modes:

(1) Automatically end method

The auto end method is to use the interrupt response signal  The trailing edge of the second negative pulse clears the interrupt service flag in the ISR.

The trailing edge of the second negative pulse clears the interrupt service flag in the ISR.

The end of this interrupt service is done automatically by the hardware. Note that the clearing of the "1" bit in the ISR is done during the interrupt response process, not the actual end of the interrupt service routine, if the service is interrupted. During the execution of the program, there is another request signal with a lower priority than the current interrupt, because the 8259A does not save any flags to indicate that the current service has not yet ended, causing the low-priority interrupt request to enter and disturb the service program, so this This method is only suitable for use without interrupted nesting.

(2) Ordinary end method

The normal end method is to send a normal EOI (endofinterrupt) command to the 8259A by writing a write operation command word OCW2 in the interrupt service routine (it does not specify the interrupt level number to be reset) to clear the current highest priority bit in the ISR.

Since this end method is to clear the one with the highest priority in the ISR, it is suitable to use the interrupt in the fully nested mode to end. Because in the completely nested mode, the interrupt priority is fixed, the 8259A always responds to the highest priority interrupt. The corresponding bit of the highest priority stored in the ISR must correspond to the service program being executed.

(3) Special ending method

The special end mode is to clear the specified bit in the ISR by sending a special EOI command (specifying the interrupt level to be reset) to the 8259A by programming the write operation command word OCW2 in the interrupt service routine.

Since it is explicitly pointed out in the special EOI command which bit in the ISR is reset, no error occurs due to the nested structure. Therefore, it can be used to complete the end of the interrupt in the fully nested mode, and is more suitable for the end of the interruption of the nested structure may be destroyed.

5. Interrupt trigger modeThe 8259A interrupt request input terminal IR7~IR0 can be triggered by two types, level trigger and edge trigger. It is set by the LTIM bit in the initialization command word ICW1.

When LTIM is set to 1, it is level-triggered, and the 8259A generates an interrupt when it detects that the IRi (i=0 to 7) is high. In this triggering mode, the required trigger level must be held to the interrupt response signal  When it is valid, and after the CPU responds to the interruption, the request signal should be revoked in time to prevent the CPU from responding again and a repeated interruption occurs.

When it is valid, and after the CPU responds to the interruption, the request signal should be revoked in time to prevent the CPU from responding again and a repeated interruption occurs.

When LTIM is set to 0, it is an edge-triggered mode. When the 8259A detects a low-to-high transition on the IRi, it generates an interrupt.

Car Phone Holder,Mobile Holder For Cars,Mobile Phone Holder For Dashboard,Mobile Phone Holder For Car Dashboard

Ningbo Luke Automotive Supplies Ltd. , https://www.car-phone-holder.com