This article is mainly about the introduction of NOR Flash, and focuses on the NOR Flash read and write principle and drive in detail.

NOR FlashNOR Flash is one of the two main non-volatile flash memory technologies currently on the market. Intel first developed the NOR Flash technology in 1988, which completely changed the original EPROM (Erasable Programmable Read-Only-Memory) and EEPROM (Electrically Erasable Programmable Read-Only Memory). The situation that dominates the world. Then, in 1989, Toshiba announced the NAND Flash structure, emphasizing lower cost per bit, higher performance, and easy upgrade through the interface like a disk. The characteristic of NOR Flash is the execution in the chip (XIP, eXecute In Place), so that the application program can run directly in the Flash flash memory without reading the code into the system RAM. The transmission efficiency of NOR is very high, and it is very cost-effective in the small capacity of 1~4MB, but the very low writing and erasing speed greatly affects its performance. The structure of NAND can provide extremely high cell density, can reach high storage density, and the speed of writing and erasing is also very fast. The difficulty in applying NAND is that the management of Flash requires a special system interface. Generally, the reading speed of NOR is slightly faster than that of NAND, and the writing speed of NAND is much faster than NOR. These conditions should be considered in the design. ——"ARM Embedded Linux System Development From Entry to Proficiency", edited by Li Yafeng, Owensheng and others, Tsinghua University Press P52 Annotated API Key

Performance comparison

Flash flash memory is a non-volatile memory, which can erase and reprogram memory cell blocks called blocks. The write operation of any flash device can only be performed in empty or erased cells, so in most cases, the erase must be performed before the write operation. It is very simple for NAND devices to perform an erase operation, while NOR requires that all bits in the target block be written as 0 before erasing.

Since NOR devices are erased in blocks of 64-128KB, the time to perform a write/erase operation is 5s. On the contrary, erasing NAND devices is performed in blocks of 8-32KB, and perform the same The operation only takes 4ms at most.

The difference in block size when performing erase further widens the performance gap between NOR and NAND. Statistics show that for a given set of write operations (especially when updating small files), more erase operations must be performed Performed in NOR-based units. In this way, when choosing a storage solution, the designer must weigh the following factors.

l The read speed of NOR is slightly faster than that of NAND.

2. The writing speed of NAND is much faster than that of NOR.

3. NAND's 4ms erasing speed is much faster than NOR's 5s.

4. Most write operations need to be erased first.

5. The erasing unit of NAND is smaller, and the corresponding erasing circuit is less.

Detailed

NOR and NAND are the two main non-volatile flash memory technologies currently on the market. Intel first developed the NOR flash technology in 1988, which completely changed the original dominance of EPROM and EEPROM. Then, in 1989, Toshiba announced the NAND flash structure, emphasizing lower cost per bit, higher performance, and can be easily upgraded through an interface like a disk. But after more than ten years, there are still quite a few hardware engineers who can't distinguish between NOR and NAND flash memory.

Like "flash memory" can often be used interchangeably with the phase "NOR memory". Many people in the industry are also confused about the advantages of NAND flash memory technology over NOR technology, because in most cases flash memory is only used to store a small amount of code, NOR flash memory is more suitable at this time. And NAND is an ideal solution for high data storage density.

The characteristic of NOR is the execution on the chip (XIP, eXecute In Place), so that the application program can be run directly in the flash memory without reading the code into the system RAM. The transmission efficiency of NOR is very high, and it is very cost-effective in the small capacity of 1 to 4MB, but the very low writing and erasing speed greatly affects its performance.

NAND structure can provide extremely high cell density, can reach high storage density, and the speed of writing and erasing is also very fast. The difficulty of applying NAND is that the management of flash requires a special system interface.

Interface difference

NOR flash has an SRAM interface, there are enough address pins to address, you can easily access every byte inside.

NAND devices use complex I/O ports to serially access data, and the methods of each product or manufacturer may vary. 8 pins are used to transmit control, address and data information.

NAND read and write operations use 512-byte blocks, which is a bit like a hard disk to manage such operations. Naturally, NAND-based memory can replace hard disks or other block devices.

Capacity costedit

The cell size of NAND flash is almost half of that of NOR devices. Due to the simpler production process, the NAND structure can provide higher capacity within a given mold size, which reduces the price accordingly.

NOR flash occupies most of the flash memory market with a capacity of 1 to 16MB, while NAND flash is only used in products with a capacity of 8 to 128MB. This also shows that NOR is mainly used in code storage media, NAND is suitable for data storage, and NAND is used in CompactFlash, Secure Digital, PC Cards and MMC (Multi Media Card) have the largest market share in the memory card market.

Reliable and durable

One important consideration when using flash media is reliability. For systems that need to expand MTBF (Mean Time Between Failures), Flash is a very suitable storage solution. The reliability of NOR and NAND can be compared in terms of life (endurance), bit swapping, and bad block handling.

Life (durability)

In NAND flash memory, the maximum number of erasing and writing of each block is one million, while the number of erasing and writing of NOR is 100,000. In addition to NAND memory having the advantage of a block erase cycle of 10 to 1, the typical NAND block size is one-eighth of the NOR device, and each NAND memory block has fewer deletes in a given time.

NOR Flash read and write principle and driveOne. principle

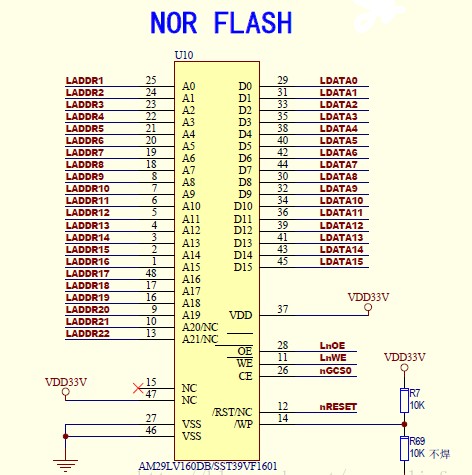

From the schematic diagram, we can see that NOR FLASH has an address line and a data line, which can read the same as the memory, but cannot write the same as the memory (some commands need to be issued). This also makes the NOR data very reliable, so it is generally used to store the bootloader. Of course, there are only nand flash on mobile phones now, which saves costs. In the next section, I will take you to analyze the nand flash driver and make a summary.

two. driver

/*

* Refer to drivers\mtd\maps\physmap.c

*/

#include "linux/module.h"

#include "linux/types.h"

#include "linux/kernel.h"

#include "linux/init.h"

#include "linux/slab.h"

#include "linux/device.h"

#include "linux/platform_device.h"

#include "linux/mtd/mtd.h"

#include "linux/mtd/map.h"

#include "linux/mtd/partitions.h"

#include "asm/io.h"

static struct map_info *s3c_nor_map;

static struct mtd_info *s3c_nor_mtd;

/*Partition array*/

static struct mtd_partition s3c_nor_partsï¼»] = {

[0] = {

.name = "bootloader_nor",

.size = 0x00040000,

.offset = 0,

},

[1] = {

.name = "root_nor",

.offset = MTDPART_OFS_APPEND, //Follow the previous one

.size = MTDPART_SIZ_FULL, //to the end

}

};

static int s3c_nor_init(void) //Entry function

{

/* 1. Allocate map_info structure */

s3c_nor_map = kzalloc(sizeof(struct map_info), GFP_KERNEL);;

/* 2. Settings: physical base address (phys), size (size), bit width (bankwidth), virtual base address (virt) */

s3c_nor_map-》name = "s3c_nor";

s3c_nor_map-》phys = 0; //Physical address

s3c_nor_map-》size = 0x1000000; /* 》= the true size of NOR*/

s3c_nor_map-》bankwidth = 2; //Bit width

s3c_nor_map-》virt = ioremap(s3c_nor_map-》phys, s3c_nor_map-》size); //Virtual address

simple_map_init(s3c_nor_map); //simple initialization

/* 3. Use: call the function provided by the NOR FLASH protocol layer to identify */

printk("use cfi_probe");

s3c_nor_mtd = do_map_probe("cfi_probe", s3c_nor_map);

/*If not recognized, use jedec*/

if (! s3c_nor_mtd)

{

printk("use jedec_probe");

s3c_nor_mtd = do_map_probe("jedec_probe", s3c_nor_map);

}

/*If it's still okay, don't release it and return an error*/

if (! s3c_nor_mtd)

{

iounmap (s3c_nor_map-" virt);

kfree(s3c_nor_map);

return -EIO;

}

/* 4. add_mtd_partitions (add partition)*/

add_mtd_partitions(s3c_nor_mtd, s3c_nor_parts, 2);

return 0;

}

static void s3c_nor_exit(void) //Exit function

{

del_mtd_partitions(s3c_nor_mtd);

iounmap (s3c_nor_map-" virt);

kfree(s3c_nor_map);

}

module_init(s3c_nor_init);

module_exit(s3c_nor_exit);

MODULE_LICENSE("GPL");

three. Drive analysis

1. Allocate map_info structure

2. Settings: physical base address (phys), size (size), bit width (bankwidth), virtual base address (virt)

3. Use: call the function provided by the NOR FLASH protocol layer to identify

4. add_mtd_partitions (add partitions)

In fact, our driver mainly writes out the differences in hardware, and most of the working kernel has been done for us. Now I will mainly analyze the third step. cfi and jedec, here is the main analysis of cfi

/*NOR FLASH recognition process*/

do_map_probe("cfi_probe", s3c_nor_map);

drv = get_mtd_chip_driver(name)

ret = drv-》probe(map); // cfi_probe.c

cfi_probe

mtd_do_chip_probe(map, &cfi_chip_probe);

cfi = genprobe_ident_chips(map, cp);

genprobe_new_chip (map, cp, &cfi)

cp-》probe_chip (map, 0, NULL, cfi)

cfi_probe_chip

// Enter CFI mode

cfi_send_gen_cmd (0x98, 0x55, base, map, cfi, cfi-"device_type, NULL);

// see if you can read "QRY"

qry_present(map, base, cfi)

The operation we are doing has actually been written for us at the protocol layer, and what we need to provide is actually the difference in hardware. Because all NOR supports this protocol.

ConclusionThis is the end of the related introduction about NOR Flash. Please correct me if there are any deficiencies.

Related reading recommendations: Detailed explanation of the difference between NAND flash and NOR flash

Related reading recommendations: a detailed analysis of the difference between NorFlash and NandFlash

SDEC 201-400KW Diesel Generator

Sdec 201-400Kw Diesel Generato,Sdec 320Kw Diesel Genset,Sdec 350Kw Diesel Genset,Sdec 250Kw Diesel Genset

Shanghai Kosta Electric Co., Ltd. , https://www.ksdpower.com