The Cortex-M processor family includes the widely used Cortex-M3 processor, the Cortex-M1 processor for FPGAs, the Cortex-M0 processor (the smallest ARM processor) introduced in early 2009, and the Co tex- introduced in early 2010. M4 processor (supports floating point and digital signal processing enhancement instructions). These processors feature advanced features and an easy-to-use programming model that are attractive for developers who want to migrate from an 8051 microcontroller to an ARM architecture. This article is an introductory guide to help developers of 8051 microcontrollers understand the major differences in architecture, software, and hardware design between the 8051 and ARM Cor tex-M processor families to speed up the migration process.

Architecture overviewFor some embedded programmers (especially those who are used to programming in assembly language), the first thing to do is to understand the programming model.

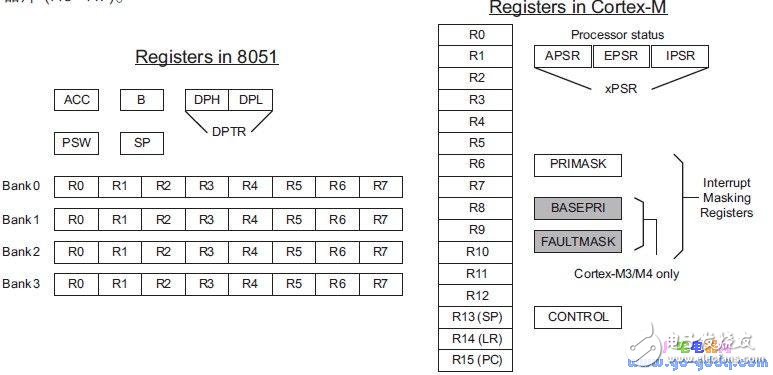

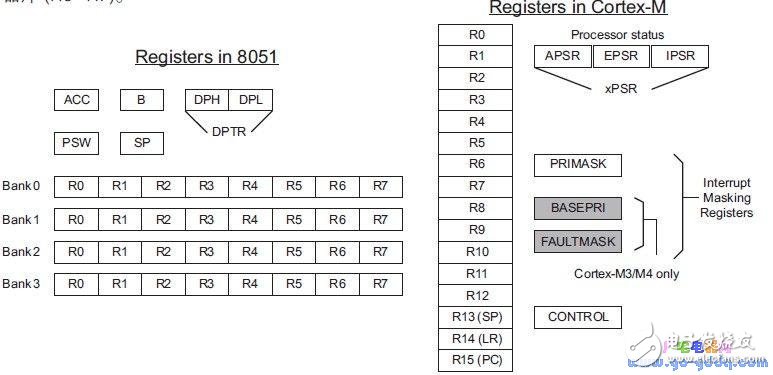

registerThe ARM Cortex-M processor has a 32-bit register bank and an xPSR (combiner status register). The 8051 has an ACC (accumulator), B, DPTR (data pointer), P SW (processor status word) and four register banks (R0-R7) each containing eight registers.

In the 8051, some instructions frequently use certain registers, such as ACC and DPTR.

This correlation can greatly degrade the performance of the system, and in ARM processors, instructions can use different registers for data processing, memory access, and use as memory pointers, so there is no such problem.

Fundamentally, the ARM architecture is a load-based (Load) and storage (STore)-based RI SC architecture. The processor registers load data and then pass the data to the A LU for single-cycle execution. The 8051 registers (ACC, B, PSW, SP, and DPTR) are accessible in the memory space of the SFR (Special Function Register).

To ensure that normal C functions can be used as interrupt handlers, the registers of the Corte x-M (R 0 - R 3, R12, LR, PC, and xPSR) are automatically pushed onto the stack when the interrupt needs to be processed, and the software Simply push other registers onto the stack as necessary. Although the 8051 has four register banks, the ACC, B, DPTR, and PSW registers are not automatically pushed, so it is usually necessary to software stack these registers through an interrupt handler.

registerThe ARM processor has 32-bit addressing for a 4GB linear memory space. This memory space is structurally divided into multiple zones. Each zone has its own recommended usage (although not fixed). The unified memory architecture not only increases the flexibility of memory usage, but also reduces the complexity of using different data types for different memory spaces.

Conversely, the 8051 microcontroller has multiple memory spaces. The partitioning of memory space makes it difficult to effectively utilize the full memory space, and C language extensions are needed to handle different memory types.

8 0 51 supports up to * KB of program memory and 64K B of data memory in the external RAM memory space. In theory, memory paging can be used to extend program memory size. However, the memory paging solution is not standardized. In other words, the implementation of memory paging by different 8051 vendors is not the same. Not only does this increase the complexity of software development, but it also significantly reduces software performance due to the software overhead required to handle page switching.

On the AR MC or tex-M3 or M4, both the SRAM area and the peripheral area provide a 1 MB bit band regiON. This bit segment area allows access to each bit within it through an alias address. Since the bit segment alias address can be accessed only by ordinary memory access instructions, the C language can be fully supported without any special instructions. The 8051 provides a small amount of bit-addressable memory (16 bytes on internal RAM and 16 bytes on SFR space). Special instructions are required to process these bit data, and C language extensions are required in the C compiler to support this feature.

The memory map of the ARMC ort ex-M processor contains multiple built-in peripheral blocks. For example, one feature of the ARM Cortex-M processor is a Nested Vectored Interrupt Controller (NVIC). In addition, there are several specified control registers and debug components in the memory map in the system area to ensure excellent interrupt handling and great convenience for developers.

The KSPOWER brand H series - 5 in 1 dimmable led driver provides 0-10V 1-10V triac/phase resistance pwm dimmable constant voltage single output LED Drivers with 5 years warranty. The low voltage lighting transformer can make the output wattage of MAX 320W and accept 12Volt, 24Volt, 36Volt and 48Volt output voltage optional. The led downlight driver is Class 2 Class P rated, and both UL/cUL, FCC CE ENEC GS Listed and SELV style enclosures. The PWM LED driver is flicker free design and protections for short circuit, over load, over voltage and over temperature. The outdoor lighting transformers use low profile aluminum metal housing with IP65 IP67 rating environment protection for indoor or outdoor use, with junction box makes 0-10V 1-10V phase pwm dimming led driver the power solutions for LED strips, LED signs, billboard and landscape lighting. The led dimmable driver featuring built-in PFC function more than 0.95 and outstanding led dimming performance.

low voltage lighting transformer, outdoor lighting transformers, transformer driver, led dimmable driver, led downlight driver

Shenzhenshi Zhenhuan Electronic Co., Ltd , https://www.szzhpower.com